芯片制造的精密藝術(shù) 從晶圓到集成電路的復(fù)雜交響

芯片,這個現(xiàn)代科技的基石,其尺寸雖常以納米計,但其制造過程卻堪稱人類工業(yè)文明中最為精密和復(fù)雜的壯舉之一。這一過程的錯綜復(fù)雜,主要根植于兩大核心環(huán)節(jié):晶圓生產(chǎn)與集成電路設(shè)計。它們?nèi)缤豁憳分械膬蓚€主旋律,各自精密運作,又必須完美協(xié)同,才能最終奏響高性能芯片的樂章。

一、晶圓生產(chǎn):構(gòu)筑微觀世界的物理基石

晶圓是芯片的物理載體,通常由高純度的硅單晶柱切割而成,其表面需要達(dá)到原子級的平整度。生產(chǎn)的復(fù)雜性首先體現(xiàn)在材料的極致追求上:硅的純度要求高達(dá)99.9999999%(9N級)以上,任何微量的雜質(zhì)都可能成為芯片中的致命缺陷。

生產(chǎn)過程本身更是一系列尖端物理與化學(xué)工藝的集成:

- 拉晶:在高溫下,從熔融的超純硅中緩慢提拉出完美的單晶硅棒,其晶體取向必須精確控制。

- 切片與研磨拋光:將硅棒切割成不足一毫米厚的薄片,并經(jīng)過精密研磨和化學(xué)機械拋光(CMP),使其表面如鏡面般光滑。

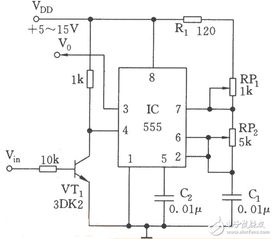

- 薄膜沉積與光刻:這是最核心的步驟。在晶圓上依次沉積導(dǎo)體、絕緣體或半導(dǎo)體薄膜,然后通過光刻技術(shù),使用掩膜版和極紫外(EUV)等先進(jìn)光源,將集成電路的圖形“印刷”到光刻膠上。這一步的精度決定了晶體管的尺寸,目前最先進(jìn)的工藝已進(jìn)入3納米以下領(lǐng)域,相當(dāng)于在頭發(fā)絲橫截面上建造數(shù)十座立交橋。

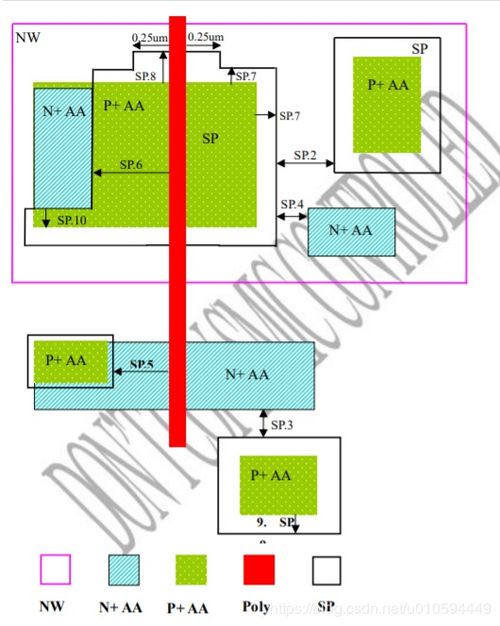

- 刻蝕與離子注入:根據(jù)光刻后的圖形,通過干法或濕法刻蝕去除特定區(qū)域的材料,并通過離子注入精確摻雜雜質(zhì),以形成晶體管所需的P區(qū)和N區(qū)。

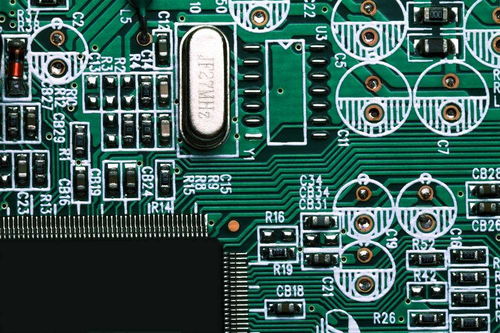

- 重復(fù)與互連:上述過程需要重復(fù)數(shù)十次,層層疊加,最終通過金屬互連層(如同微觀的金屬導(dǎo)線)將數(shù)十億甚至數(shù)百億個晶體管連接起來。

整個過程需要在超凈無塵的環(huán)境中完成,一粒微塵就可能導(dǎo)致整片晶圓報廢。工藝參數(shù)的調(diào)控要求極其嚴(yán)苛,溫度、氣壓、化學(xué)試劑濃度等任何微小偏差都會影響最終性能。

二、集成電路設(shè)計:定義芯片功能的靈魂藍(lán)圖

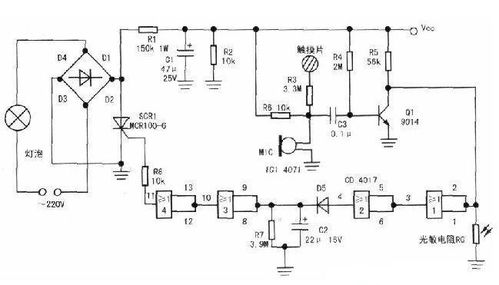

如果說晶圓生產(chǎn)是“建造”,那么集成電路設(shè)計就是“藍(lán)圖繪制”。它的復(fù)雜性在于,要在指甲蓋大小的面積上,合理規(guī)劃并驗證數(shù)十億個晶體管的行為,確保它們協(xié)同工作以實現(xiàn)預(yù)定功能(如計算、存儲、信號處理)。

設(shè)計流程是一個從抽象到具體、層層細(xì)化的過程:

- 系統(tǒng)架構(gòu)與功能定義:根據(jù)芯片用途(如CPU、GPU、AI加速器),確定整體架構(gòu)、核心模塊和性能指標(biāo)。

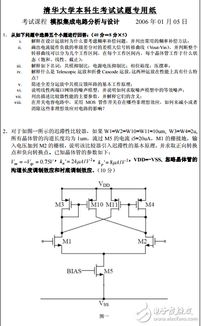

- 邏輯設(shè)計:使用硬件描述語言(如Verilog、VHDL)將功能轉(zhuǎn)化為寄存器傳輸級(RTL)描述,即用代碼定義數(shù)字電路的邏輯行為。

- 邏輯綜合與驗證:通過電子設(shè)計自動化(EDA)工具,將RTL代碼“編譯”成由基本邏輯門(如與門、或門)組成的網(wǎng)表,并進(jìn)行嚴(yán)格的功能仿真和形式驗證,確保邏輯正確。

- 物理設(shè)計:這是將邏輯網(wǎng)表轉(zhuǎn)化為實際物理版圖的關(guān)鍵一步,包括:

- 布局:決定每個邏輯單元在芯片上的具體位置。

- 布線:在多層金屬層上,規(guī)劃并連接所有單元之間的導(dǎo)線,猶如在極度擁擠的立體城市中規(guī)劃所有道路,需滿足時序、信號完整性、功耗和面積等無數(shù)約束。

- 時序與物理驗證:使用復(fù)雜模型分析信號延遲,確保芯片能在目標(biāo)頻率下穩(wěn)定運行,并進(jìn)行設(shè)計規(guī)則檢查(DRC)和版圖與電路圖一致性檢查(LVS),確保版圖符合晶圓廠的制造工藝要求。

設(shè)計的復(fù)雜性隨著晶體管數(shù)量指數(shù)級增長而劇增。布線擁塞、功耗墻、散熱、信號串?dāng)_等問題都需要精密的算法和強大的EDA工具來解決。一個現(xiàn)代高端芯片的設(shè)計成本可能高達(dá)數(shù)億美元,涉及數(shù)千名工程師的協(xié)同工作。

三、協(xié)同與迭代:復(fù)雜性的倍增

晶圓生產(chǎn)(制造)與集成電路設(shè)計并非孤立環(huán)節(jié),它們之間存在深度的協(xié)同與迭代,這進(jìn)一步放大了整體的復(fù)雜性。

- 設(shè)計-工藝協(xié)同優(yōu)化(DTCO):設(shè)計師必須深刻理解制造工藝的細(xì)節(jié)和極限(如最小線寬、材料特性),而制造工藝的進(jìn)步(如采用新材料、新結(jié)構(gòu))也需要設(shè)計方法的相應(yīng)革新。例如,F(xiàn)inFET、GAA晶體管等新結(jié)構(gòu)的引入,直接改變了物理設(shè)計規(guī)則。

- 可制造性設(shè)計(DFM):在設(shè)計階段就必須考慮如何提高芯片在制造過程中的良率。例如,增加冗余電路、優(yōu)化圖形以降低光刻難度、避免容易出現(xiàn)制造缺陷的版圖圖案等。

- 漫長的反饋循環(huán):從設(shè)計完成到流片(Tape-out)制造出第一批樣品,再到測試、發(fā)現(xiàn)問題、修改設(shè)計、重新流片,周期漫長且成本極高。任何一方的誤差或 mismatch 都可能導(dǎo)致項目失敗。

因此,芯片制造的“錯綜復(fù)雜”,本質(zhì)上是微觀尺度上物理實現(xiàn)的極限挑戰(zhàn)(晶圓生產(chǎn))與宏觀系統(tǒng)級功能規(guī)劃的極致抽象(集成電路設(shè)計)兩者結(jié)合所必然產(chǎn)生的復(fù)雜性。它代表了材料科學(xué)、精密制造、物理學(xué)、化學(xué)、計算機科學(xué)、電子工程等多個學(xué)科頂尖智慧的融合。每一枚小小芯片的誕生,都是一場跨越設(shè)計與制造鴻溝的精密交響,是人類探索和掌控微觀世界能力的集中體現(xiàn)。隨著摩爾定律的持續(xù)推進(jìn),這場交響樂將演奏出愈加復(fù)雜而美妙的樂章,持續(xù)驅(qū)動著整個數(shù)字時代的演進(jìn)。

如若轉(zhuǎn)載,請注明出處:http://m.lj555.cn/product/73.html

更新時間:2026-04-26 14:30:57