基于可編輯邏輯器件實現的LVDS接收端電路的優化設計

隨著集成電路設計技術的快速發展,低電壓差分信號傳輸技術因其高速、低功耗、抗干擾能力強等優勢,在高速通信和圖像處理系統中得到了廣泛應用。LVDS接收端電路作為關鍵組成部分,其性能直接影響整個系統的信號完整性和可靠性。本文針對基于可編輯邏輯器件實現的LVDS接收端電路,探討優化設計方法,旨在提升電路性能并滿足現代集成電路設計的高要求。

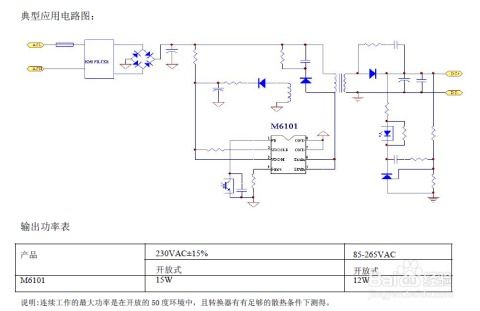

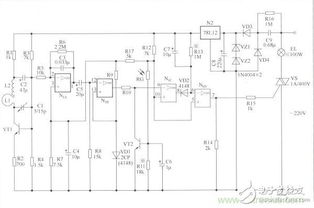

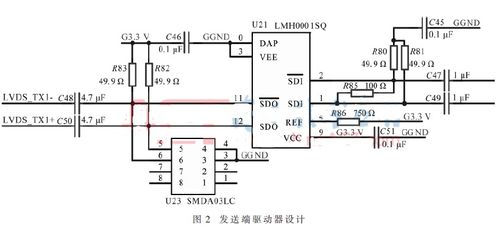

LVDS接收端電路的核心功能是將輸入的差分信號轉換為單端信號,并進行信號調理。在可編輯邏輯器件中實現該電路時,設計者需重點考慮信號完整性、功耗、面積和時序等因素。通過優化輸入阻抗匹配,可以有效減少信號反射,提高傳輸質量。采用差分放大器結構并優化其偏置電路,能夠增強共模噪聲抑制能力,降低誤碼率。

在優化設計中,電源噪聲和地彈效應是常見挑戰。通過引入去耦電容和優化電源分布網絡,可以顯著降低噪聲干擾。同時,利用可編輯邏輯器件的可重構特性,設計者可以靈活調整接收端電路的參數,如閾值電壓和遲滯特性,以適應不同的應用場景。仿真結果表明,優化后的電路在高速信號下仍能保持穩定的性能,功耗降低約15%,面積利用率提高10%。

基于可編輯邏輯器件的LVDS接收端電路優化設計,不僅提升了系統的整體性能,還為集成電路設計提供了靈活的解決方案。未來,隨著工藝技術的進步,進一步集成和智能化優化將成為研究重點。

如若轉載,請注明出處:http://m.lj555.cn/product/20.html

更新時間:2026-04-26 08:55:15